台积电周二更新了其制程工艺路线图,称其4纳米工艺芯片将在2021年底进入“风险生产”阶段,并于2022年实现量产。3纳米产品预计在2022年下半年投产, 2纳米工艺正在开发中。在产能方面,没有任何竞争对手能威胁到台积电的主导地位,而且未来几年内也不会。

至于制造技术,台积电最近重申,它有信心其2纳米(N2)、3纳米(N3)和4纳米(N4)工艺将按时推出,并保持比竞争对手更先进节点工艺领先优势。

今年早些时候,台积电将2021年的资本支出预算大幅提高到250亿至280亿美元,最近更是追加到300亿美元左右。这是台积电未来三年增加产能和研发投入计划的一部分,该公司计划三年总共投资1000亿美元。

在台积电今年300亿美元的资本预算中,约80%将用于扩大先进技术的产能,如3纳米、4纳米、5纳米、6纳米以及7纳米芯片。华兴证券分析师认为,到今年年底,先进节点上的大部分资金将用于将台积电的5纳米产能扩大到每月11万至12万片晶圆。

与此同时,台积电表示,其资本支出的10%将用于先进的封装和掩模制造,另外10%将用于支持专业技术开发,包括成熟节点的定制版本。

台积电最近提高资本支出的举措是在英特尔宣布其IDM 2.0战略(涉及内部生产、外包和代工运营)之后做出的,并在很大程度上重申了该公司在竞争加剧之际对短期和长期未来的信心。

台积电总裁兼首席执行官魏哲家在最近与分析师和投资者的电话会议上表示:“作为一家领先的晶圆代工企业,台积电在成立30多年的历史中从未缺乏竞争,但我们知道如何竞争。我们将继续专注于提供领先的技术、卓越的制造服务,并赢得客户的信任。其中,赢得客户信任是相当重要的,因为我们没有与客户竞争的内部产品。”

(来自:AnandTech)

N5工艺赢得客户信赖

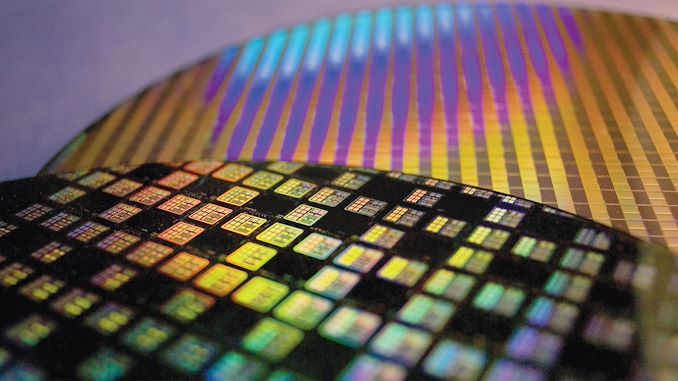

台积电是2020年中期第一家开始使用其N5工艺技术进行大规模芯片制造(HVM)的公司。最初,该节点仅用于为台积电的最重要客户服务,即苹果和海思。如今,随着更多客户已经准备好各自的N5规格芯片设计,因此该节点的采用正在增长。与此同时,台积电表示,计划使用N5系列技术(包括N5、N5P和N4)的客户比几个月前预计的要多。

魏哲家说:“N5已经进入量产的第二个年头,产量比我们最初的计划要高。在智能手机和高性能计算(HPC)应用的推动下,N5的需求继续强劲,我们预计2021年N5将贡献晶圆收入的20%左右。事实上,我们看到N5和N3的客户越来越多。需求如此之高,我们必须准备好应对的准备。”

对于台积电来说,HPC应用包括许多不同类型的产品,比如AI加速器、CPU、GPU、FPGA、NPU和视频游戏SoC等。由于台积电只是代工制造商,不会透露它使用哪种节点生产的产品,但N5在HPC领域的采用率正在增长这一事实非常重要。

魏哲家表示:“我们预计,在智能手机和HPC应用需求强劲的推动下,未来几年对我们N5系列的需求将继续增长。我们预计HPC不仅会在第一波增长中出现,实际上还会在更多的需求波中出现,以支持我们未来领先的N5节点。”

台积电N5在尖端技术采用者中的市场份额正在增加,这并不特别令人惊讶。华兴资本分析师估计,台积电N5的晶体管密度约为每平方毫米1.7亿个晶体管,这将使其成为当今可用密度最高的技术。相比之下,三星电子的5LPE每平方毫米可以容纳大约1.25亿到1.3亿个晶体管,而英特尔的10纳米节点晶体管密度大约为每平方毫米1亿个。

在接下来的几周里,台积电将开始使用其名为N5P的N5改进技术性能增强版来制造芯片,该技术承诺将频率提高至多5%,或将功耗降低至多10%。N5P为客户提供了一条无缝的迁移路径,无需大量的工程资源投资或更长的设计周期,因此任何使用N5设计的用户都可以使用N5P。例如,N5的早期采用者可以将他们的IP重新用于N5P芯片。

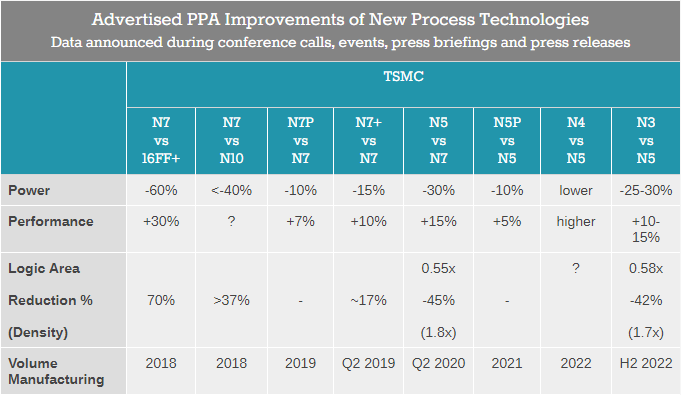

N4明年将投入量产

台积电的N5系列技术还包括将在今年晚些时候进入“风险生产”阶段,并将在2022年用于批量生产的N4工艺芯片。这项技术将提供比N5更多的PPA(功率、性能、面积)优势,但保持相同的设计规则、设计基础设施、SPICE模拟程序和IP。同时,由于N4进一步扩大了EUV光刻工具的使用范围,它还减少了掩模数量、工艺步骤、风险和成本。

魏哲家说:“N4将利用N5的强大基础进一步扩大我们的5纳米系列技术优势。N4是从N5直接迁移过来的,具有兼容的设计规则,同时为下一波5纳米产品提供进一步的性能、功率和密度增强。N4的目标是今年下半年进入风险生产阶段,2022年实现批量生产。”

到2022年N4产品投入量产时,台积电将拥有约两年的N5经验和三年的EUV经验。因此,人们的预期是,其收益率将会很高。但是,即使N4被认为是尖端的,它也不会是台积电明年提供的最先进制造技术。

N3将于2022年下半年亮相

2022年,台积电将推出其全新的N3制造工艺,该工艺将继续使用FinFET晶体管,但预计将提供一整套PPA改进方案。特别是,与目前的N5工艺相比,台积电的N3承诺将性能提高10%-15%,或者降低25%-30%的功耗。同时,根据结构的不同,新节点还将使晶体管密度提高1.1到1.7倍。

N3将进一步增加EUV层的数量,但将继续使用DUV光刻。此外,由于该技术始终在使用FinFET,它将不需要从头开始重新设计的新一代电子设计自动化(EDA)工具和开发全新的IP,相对于三星基于GAAFET/MBCFET的3GAE,这可能更具竞争优势。

魏哲家表示:“N3将是我们继N5之后的又一次全面节点跨越,它将使用FinFET晶体管结构为我们的客户提供最好的技术成熟度、性能和成本。我们的N3技术开发进展良好。与N5和N7相比,我们继续看到N3的HPC和智能手机应用客户参与度要高得多。”

事实上,台积电声称客户对N3的参与度越来越高,间接地表明了其对N3寄予了厚望。魏哲家说:“N3的风险生产预计在2021年启动,量产目标是在2022年下半年。我们的N3技术推出后,将成为PPA和晶体管技术中最先进的代工技术。我们有信心,我们的N5和N3都将成为台积电大规模和持久使用的节点工艺。”

超越N3

全栅场效应晶体管(GAAFET)仍是台积电发展路线图的重要组成部分。该公司预计将在其“后N3”技术(大概是N2)中使用全新的晶体管。事实上,台积电正处于寻找下一代材料和晶体管结构的阶段,这些材料和晶体管结构将在未来许多年内使用。

台积电在最近的年报中称:“对于先进的CMOS(互补金属氧化物半导体),台积电的3纳米和2纳米CMOS节点在流水线上进展顺利。”此外,台积电加强的探索性研发工作集中在2纳米节点、3D晶体管、新存储器和Low-R互连等领域,这些领域正在为引入许多技术平台奠定坚实的基础。

值得注意的是,台积电正在12号工厂扩大研发能力,目前正在研发N3、N2和更先进的节点。

有信心超越代工行业整体增长率

总体而言,台积电相信,其“大家的晶圆代工厂” (everyone’s foundry)战略将使其在规模、市场份额和销售额方面进一步增长。该公司还预计,未来将保持其技术领先地位,这对其增长至关重要。

台积电首席财务官黄文德最近在与分析师和投资者的电话会议上表示:“我们现在预测,2021年全年,代工行业的增长率约为16%。对于台积电来说,我们有信心能够超越晶圆代工行业的整体增长,在2021年实现20%左右的增长。”

该公司拥有强大的技术路线图,并将继续每年推出改进的前沿节点,从而以可预测的节奏为客户提供技术改进。

台积电知道如何与拥有尖端节点的竞争对手以及专注于专业工艺技术的芯片制造商竞争,因此它并不认为英特尔代工服务(IFS)是直接的威胁,特别是因为后者主要聚焦于尖端和先进的节点。

金融分析师普遍认同台积电的乐观态度,主要是因为预计该公司的N3和N5节点将不会有竞争对手提供类似的晶体管密度和晶圆产能。

华兴证券分析师表示:“继英特尔今年3月宣布的晶圆代工业务回归后,台积电愿意从2021年开始制定为期3年的1000亿美元资本支出和研发投资计划,这表明其有信心扩大代工领导地位。我们认为,随着N3和N5的出现,台积电的战略价值也在上升:HPC和智能手机应用的N5生产活动强劲,同时与N5和N7在类似阶段相比,N3客户的参与度更高。

评论(0)